### UNIT-1 BIASING OF DISCRETE BJT AND MOSFET

### DC LOAD LINE AND OPERATING POINT

For the transistor to properly operate it must be biased. There are several methods to establish the DC operating point. We will discuss some of the methods used for biasing transistors as well as troubleshooting methods used for transistor bias circuits.

The goal of amplification in most cases is to increase the amplitude of an ac signal without altering it.

Biasing in electronics is the method of establishing predetermined voltages or currents at various points of an electronic circuit for the purpose of establishing proper operating conditions in electronic components. Many electronic devices whose function is signal processing time-varying (AC) signals also require a steady (DC) current or voltage to operate correctly. The AC signal applied to them is superposed on this DC bias current or voltage. Other types of devices, for example magnetic recording heads, require a time-varying (AC) signal as bias. The operating point of a device, also known as bias point, quiescent point, or Q-point, is the steady-state voltage or current at a specified terminal of an active device (a transistor or vacuum tube) with no input signal applied

Most often, bias simply refers to a fixed DC voltage applied to the same point in a circuit as an alternating current (AC) signal, frequently to select the desired operating response of a semiconductor or other electronic component (forward or reverse bias). For example, a bias voltage is applied to a transistor in an electronic amplifier to allow the transistor to operate in a particular region of its transconductance curve. For vacuum tubes, a (much higher) grid bias voltage is also often applied to the grid electrodes for precisely the same reason.

A hot bias can lower the tube life span, but a "cool" bias can induce crossover distortion.

Bias is also the term used for a high-frequency signal added to the audio signal recorded on magnetic tape. See tape bias.

Bias is used in direct broadcast satellites such as DirecTV and Dish Network, the integrated receiver/decoder (IRD) box actually powers the feedhorn or low-noise block converter (LNB) receiver mounted on the dish arm. This bias is changed from a lower voltage to a higher voltage to select the polarization of the LNB, so that it receives signals that are polarized either horizontal or vertical, thereby allowing it to receive twice as many channels.

We still need to determine the optimal values for the DC biasing in order to choose resistors, etc. This bias point is called the quiescent or Q-point as it gives the values of the voltages when no input signal is applied. To determine the Q-point we need to look at the range of values for which the transistor is in the active region.

## **Bipolar junction transistors**

For bipolar junction transistors the bias point is chosen to keep the transistor operating in the active mode, using a variety of circuit techniques, establishing the Q-point DC voltage and current. A small signal is then applied on top of the Q-point bias voltage, thereby either modulating or switching the current, depending on the purpose of the circuit.

The quiescent point of operation is typically near the middle of the DC load line. The process of obtaining a certain DC collector current at a certain DC collector voltage by setting up the operating point is called biasing.

After establishing the operating point, when an input signal is applied, the output signal should not move the transistor either to saturation or to cut-off. However, this unwanted shift still might occur, due to the following reasons:

1. Parameters of transistors depend on junction temperature. As junction temperature increases, leakage current due to minority charge carriers ( $I_{CBO}$ ) increases. As  $I_{CBO}$  increases,  $I_{CEO}$  also

increases, causing an increase in collector current  $I_C$ . This produces heat at the collector junction. This process repeats, and, finally, the Q-point may shift into the saturation region. Sometimes, the excess heat produced at the junction may even burn the transistor. This is known as thermal runaway.

2. When a transistor is replaced by another of the same type, the Q-point may shift, due to changes in parameters of the transistor, such as current gain  $(\beta)$  which varies slightly for each unique transistor.

To avoid a shift of Q-point, bias-stabilization is necessary. Various biasing circuits can be used for this purpose.

### Load line

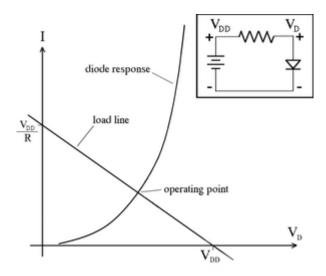

A **load line** is used in graphical analysis of nonlinear electronic circuits, representing the constraint other parts of the circuit place on a non-linear device, like a diode or transistor. It is usually drawn on a graph of the current vs the voltage in the nonlinear device, called the device's characteristic curve. A load line, usually a straight line, represents the response of the linear part of the circuit, connected to the nonlinear device in question. The operating point(s) of the circuit are the points where the characteristic curve and the load line intersect; at these points the current and voltage parameters of both parts of the circuit match.<sup>[1]</sup>

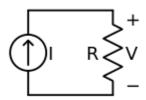

The example at right shows how a load line is used to determine the current and voltage in a simple diode circuit. The diode, a nonlinear device, is in series with a linear circuit consisting of a resistor, R and a voltage source,  $V_{DD}$ . The characteristic curve (curved line), representing current I through the diode versus voltage across the diode  $V_D$ , is an exponential curve. The load line (diagonal line) represents the relationship between current and voltage due to Kirchhoff's voltage law applied to the resistor and voltage source, is

$$V_D = V_{DD} - IR$$

Since the current going through the three elements in series must be the same, and the voltage at the terminals of the diode must be the same, the operating point of the circuit will be at the intersection of the curve with the load line.

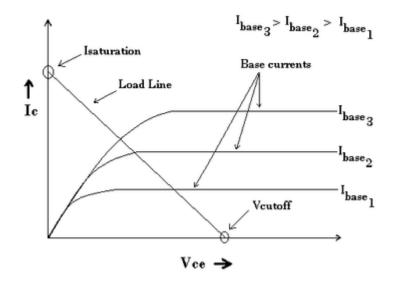

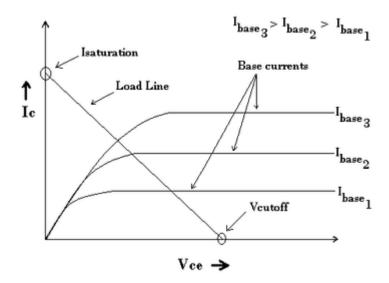

In a BJT circuit, the BJT has a different current-voltage ( $I_C$ - $V_{CE}$ ) characteristic depending on the base current. Placing a series of these curves on the graph shows how the base current will affect the operating point of the circuit.

### **Transistor load line**

Common emitter transistor load line.

The load line diagram at right is for a transistor connected in a common emitter circuit. It shows the collector current in the transistor  $I_C$  versus collector voltage  $V_{CE}$  for different values of base current  $I_{base}$ . The load line represents a particular value of collector load resistor ( $R_C$ ). The intersections of the load line with the transistor characteristic curve represent the different values of  $I_C$  and  $V_{CE}$  at different base currents.

The point on the load line where it intersects the collector current axis is referred to as saturation point. At this point, the transistor current is maximum and voltage across collector is minimum, for a given load. For this circuit,  $I_{C-SAT} = V_{CC}/R_{C}$ .

The cutoff point is the point where the load line intersects with the collector voltage axis. Here the transistor current is minimum (approximately zero) and emitter is grounded. Hence  $V_{\text{CE-CUTOFF}} = V_{\text{cc}}$ .

The operating point of the circuit in this configuration is generally designed to be in the active region, approximately between middle of the load line and close to saturation point. In this region, the collector current is proportional to the base current, and hence useful for amplifier applications. a load line is normally drawn on  $I_c$ - $V_{ce}$  characteristics curves for the transistor used in amplifier circuit.

## **Bipolar transistor biasing**

Bipolar transistor amplifiers must be properly biased to operate correctly. In circuits made with individual devices (discrete circuits), biasing networks consisting of resistors are commonly employed. Much more elaborate biasing arrangements are used in integrated circuits, for example, bandgap voltage references and current mirrors.

The operating point of a device, also known as bias point, quiescent point, or Q-point, is the point on the output characteristics that shows the DC collector–emitter voltage ( $V_{ce}$ ) and the collector current ( $I_c$ ) with no input signal applied. The term is normally used in connection with devices such as transistors.

## Bias circuit requirements

## Signal requirements for Class A amplifiers

For analog operation of a Class A amplifier, the Q-point is placed so the transistor stays in **active mode** (does not shift to operation in the saturation region or cut-off region) when input is applied. For digital operation, the Q-point is placed so the transistor does the contrary switches from the "on" (saturation) to the "off" (cutoff) state. Often, the Q-point is established near the center of the active region of a transistor characteristic to allow similar signal swings in positive and negative directions. The Q-point should be stable; in particular, it should be insensitive to variations in transistor parameters (for example, should not shift if transistor is replaced by another of the same type), variations in temperature, variations in power supply voltage and so forth. The circuit must also be practical; both easily implemented and cost-effective.

#### Thermal considerations

At constant current, the voltage across the emitter-base junction  $V_{BE}$  of a bipolar transistor decreases 2 mV (silicon) and 1.8mV

(germanium) for each 1 °C rise in temperature (reference being 25 °C). By the Ebers–Moll model, if the base–emitter voltage  $V_{BE}$  is held constant and the temperature rises, the current through the base–emitter diode  $I_B$  will increase, and thus the collector current  $I_C$  will also increase. Depending on the bias point, the power dissipated in the transistor may also increase, which will further increase its temperature and exacerbate the problem. This deleterious positive feedback results in **thermal runaway**. There are several approaches to mitigate bipolar transistor thermal runaway. For example,

- Negative feedback can be built into the biasing circuit so that increased collector current leads to decreased base current. Hence, the increasing collector current throttles its source.

- Heat sinks can be used that carry away extra heat and prevent the base–emitter temperature from rising.

- The transistor can be biased so that its collector is normally less than half of the power supply voltage, which implies that collector–emitter power dissipation is at its maximum value. Runaway is then impossible because increasing collector current leads to a decrease in dissipated power; this notion is known as the half-voltage principle.

The circuits below primarily demonstrate the use of negative feedback to prevent thermal runaway.

# Types of bias circuit for Class A amplifiers

The following discussion treats five common biasing circuits used with Class A bipolar transistor amplifiers:

- 1. Fixed bias

- 2. Collector-to-base bias

- 3. Fixed bias with emitter resistor

- 4. Voltage divider bias

- 5. Emitter bias

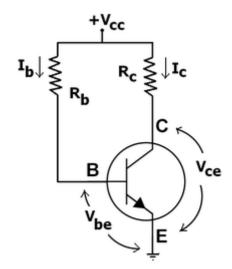

### Fixed bias (base bias)

$\Box$

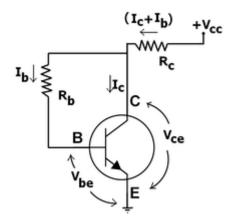

## Fixed bias (Base bias)

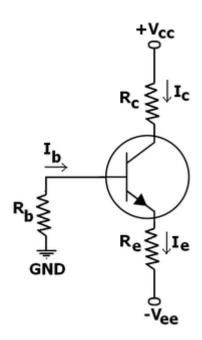

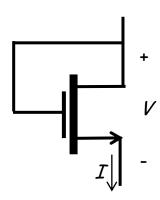

This form of biasing is also called base bias. In the example image on the right, the single power source (for example, a battery) is used for both collector and base of a transistor, although separate batteries can also be used.

In the given circuit,

$$V_{cc} \equiv I_B R_B + V_{be}$$

Therefore,

$$I_B = (V_{cc} - V_{be})/R_B$$

For a given transistor,  $V_{be}$  does not vary significantly during use. As  $V_{cc}$  is of fixed value, on selection of  $R_B$ , the base current  $I_B$  is fixed. Therefore this type is called fixed bias type of circuit.

Also for given circuit,

$$V_{cc} = I_{C}R_{C} + V_{ce}$$

Therefore,

$$V_{ce} = V_{cc}$$

-  $I_C R_C$

The common-emitter current gain of a transistor is an important parameter in circuit design, and is specified on the data sheet for a particular transistor. It is denoted as  $\beta$  on this page.

#### Because

$$I_C = \beta I_B$$

we can obtain  $I_C$  as well. In this manner, operating point given as  $(V_{ce}, I_C)$  can be set for given transistor.

#### **Merits:**

- It is simple to shift the operating point anywhere in the active region by merely changing the base resistor  $(R_B)$ .

- A very small number of components are required.

### **Demerits:**

- The collector current does not remain constant with variation in temperature or power supply voltage. Therefore the operating point is unstable.

- Changes in  $V_{be}$  will change  $I_B$  and thus cause  $I_E$  to change. This in turn will alter the gain of the stage.

- When the transistor is replaced with another one, considerable change in the value of  $\beta$  can be expected. Due to this change the operating point will shift.

- For small-signal transistors (e.g., not power transistors) with relatively high values of  $\beta$  (i.e., between 100 and 200), this configuration will be prone to thermal runaway. In particular, the stability factor, which is a measure of the change in collector current with changes in reverse saturation current, is approximately  $\beta+1$ . To ensure absolute stability of the amplifier, a stability factor of less than 25 is preferred, and so small-signal transistors have large stability factors. [citation needed]

# **Usage:**

Due to the above inherent drawbacks, fixed bias is rarely used in linear circuits (i.e., those circuits which use the transistor as a current source). Instead, it is often used in circuits where transistor is used as a switch. However, one application of fixed bias is to achieve crude automatic gain control in the transistor by feeding the base resistor from a DC signal derived from the AC output of a later stage.

### **Collector Feedback Bias**

ㅁ

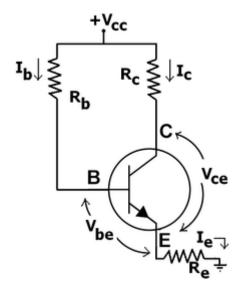

### Collector-to-base bias

This configuration employs negative feedback to prevent thermal runaway and stabilize the operating point. In this form of biasing, the base resistor  $R_{\rm B}$  is connected to the collector instead of connecting it to the DC source  $V_{\rm cc}$ . So any thermal runaway will induce a voltage drop across the  $R_{\rm C}$  resistor that will throttle the transistor's base current.

From Kirchhoff's voltage law, the voltage  $V_{\rm Rb}$ across the base resistor  $R_{\rm bis}$

$$V_{

m R_b} = V_{

m cc} - \overbrace{(I_{

m c} + I_{

m b})R_{

m c}}^{

m Voltage\ at\ base} - \overbrace{V_{

m be}}^{

m Voltage\ at\ base}.$$

By the Ebers–Moll model,  $I_c = \beta I_b$ , and so

$$V_{\rm R_b} = V_{\rm cc} - (\overbrace{\beta I_{\rm b}}^{I_{\rm c}} + I_{\rm b}) R_{\rm c} - V_{\rm be} = V_{\rm cc} - I_{\rm b} (\beta + 1) R_{\rm c} - V_{\rm be}.$$

From Ohm's law, the base current  $I_b = V_{R_b}/R_b$ , and so

$$\overbrace{I_{\rm b}R_{\rm b}}^{V_{\rm R_b}} = V_{\rm cc} - I_{\rm b}(\beta + 1)R_{\rm c} - V_{\rm be}.$$

Hence, the base current  $I_{\text{bis}}$

$$I_{\rm b} = \frac{V_{\rm cc} - V_{\rm be}}{R_{\rm b} + (\beta + 1)R_{\rm c}}$$

If  $V_{\rm be}$  is held constant and temperature increases, then the collector current  $I_{\rm c}$  increases. However, a larger  $I_{\rm c}$  causes the voltage drop across resistor  $R_{\rm c}$  to increase, which in turn reduces the voltage  $V_{\rm R_b}$  across the base resistor  $R_{\rm b}$ . A lower base-resistor voltage drop reduces the base current  $I_{\rm b}$ , which results in less collector current  $I_{\rm c}$ . Because an increase in collector current with temperature is opposed, the operating point is kept stable.

### **Merits:**

• Circuit stabilizes the operating point against variations in temperature and  $\beta$  (i.e. replacement of transistor)

### **Demerits:**

• In this circuit, to keep  $I_c$  independent of  $\beta$ , the following condition must be met:

$$I_{\rm c} = \beta I_{\rm b} = \frac{\beta (V_{\rm cc} - V_{\rm be})}{R_{\rm b} + R_{\rm c} + \beta R_{\rm c}} \approx \frac{(V_{\rm cc} - V_{\rm be})}{R_{\rm c}}$$

which is the case when

$$\beta R_{\rm c} \gg R_{\rm b}$$

.

- As  $\beta$ -value is fixed (and generally unknown) for a given transistor, this relation can be satisfied either by keeping  $R_c$  fairly large or making  $R_b$ very low.

- o If  $R_{cis}$  large, a high  $V_{ccis}$  necessary, which increases cost as well as precautions necessary while handling.

- $_{\circ}$  If  $R_{\text{b}}$  is low, the reverse bias of the collector—base region is small, which limits the range of collector voltage swing that leaves the transistor in active mode.

- The resistor  $R_b$  causes an AC feedback, reducing the voltage gain of the amplifier. This undesirable effect is a trade-off for greater Q-point stability.

**Usage:** The feedback also decreases the input impedance of the amplifier as seen from the base, which can be advantageous. Due to the gain reduction from feedback, this biasing form is used only when the trade-off for stability is warranted.

### Fixed bias with emitter resistor

ㅁ

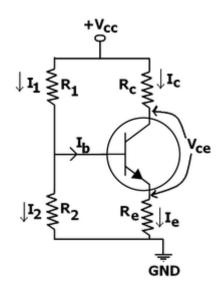

### Fixed bias with emitter resistor

The fixed bias circuit is modified by attaching an external resistor to the emitter. This resistor introduces negative feedback that stabilizes the Q-point. From Kirchhoff's voltage law, the voltage across the base resistor is

$$V_{R_b} = V_{CC} - I_e R_e - V_{be}$$

From Ohm's law, the base current is

$$I_b = \frac{V_{R_b}}{R_b}$$

The way feedback controls the bias point is as follows. If  $V_{be}$  is held constant and temperature increases, emitter current increases. However, a larger  $I_e$  increases the emitter voltage  $V_e = I_e R_e$ , which in turn reduces the voltage  $V_{Rb}$  across the base resistor. A lower base-resistor voltage drop reduces the base current, which results in less collector current because  $I_c = \beta I_B$ . Collector current and emitter current are related by  $I_c = \alpha I_e$  with  $\alpha \approx 1$ , so the increase in emitter current with temperature is opposed, and the operating point is kept stable.

Similarly, if the transistor is replaced by another, there may be a change in  $I_C$  (corresponding to change in  $\beta$ -value, for example). By similar process as above, the change is negated and operating point kept stable.

For the given circuit,

$$I_B = \frac{V_{CC} - V_{be}}{R_B + (\beta + 1)R_E}$$

### **Merits:**

The circuit has the tendency to stabilize operating point against changes in temperature and  $\beta$ -value.

### **Demerits:**

• In this circuit, to keep  $I_C$  independent of  $\beta$  the following condition must be met:

$$I_C = \beta I_B = \frac{\beta (V_{CC} - V_{be})}{R_B + (\beta + 1)R_E} \approx \frac{(V_{CC} - V_{be})}{R_E}$$

which is approximately the case if

$$(\beta + 1)R_E \gg R_B$$

- As  $\beta$ -value is fixed for a given transistor, this relation can be satisfied either by keeping  $R_E$  very large, or making  $R_B$  very low.

- $_{\circ}$  If  $R_{\rm E}$  is of large value, high  $V_{\rm CC}$  is necessary. This increases cost as well as precautions necessary while handling.

- If R<sub>B</sub> is low, a separate low voltage supply should be used in the base circuit. Using two supplies of different voltages is impractical.

- In addition to the above, R<sub>E</sub> causes ac feedback which reduces the voltage gain of the amplifier.

## **Usage:**

The feedback also increases the input impedance of the amplifier when seen from the base, which can be advantageous. Due to the above disadvantages, this type of biasing circuit is used only with careful consideration of the trade-offs involved.

Collector-Stabilized Biasing

# Voltage divider biasing

#### ㅁ

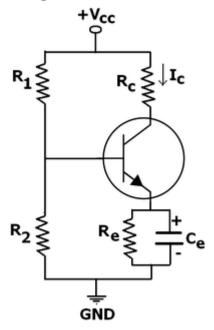

# Voltage divider bias

The voltage divider is formed using external resistors  $R_1$  and  $R_2$ . The voltage across  $R_2$  forward biases the emitter junction. By proper selection of resistors  $R_1$  and  $R_2$ , the operating point of the transistor can be made independent of  $\beta$ . In this circuit, the voltage divider holds the base voltage fixed independent of base current provided the divider current is large compared to the base current. However, even with a fixed base voltage, collector current varies with temperature (for example) so an emitter resistor is added to stabilize the Q-point, similar to the above circuits with emitter resistor.

In this circuit the base voltage is given by:

$$V_B = \text{voltage across } R_2 = V_{cc} \frac{R_2}{(R_1 + R_2)} - I_B \frac{R_1 R_2}{(R_1 + R_2)}$$

$$\approx V_{cc} \frac{R_2}{(R_1 + R_2)_{\text{provided }} I_B << I_2 = V_B / R_2.}$$

Also

$$V_B = V_{be} + I_E R_E$$

For the given circuit,

$$I_B = \frac{\frac{V_{CC}}{1 + R_1/R_2} - V_{be}}{(\beta + 1)R_E + R_1 \parallel R_2}.$$

### **Merits:**

- Unlike above circuits, only one dc supply is necessary.

- Operating point is almost independent of  $\beta$  variation.

- Operating point stabilized against shift in temperature.

### **Demerits:**

• In this circuit, to keep  $I_C$  independent of  $\beta$  the following condition must be met:

$$I_C = \beta I_B = \beta \frac{\frac{V_{CC}}{1 + R_1/R_2} - V_{be}}{(\beta + 1)R_E + R_1 \parallel R_2} \approx \frac{\frac{V_{CC}}{1 + R_1/R_2} - V_{be}}{R_E},$$

which is approximately the case if

$$(\beta + 1)R_E >> R_1 \parallel R_2$$

where  $R_1 \parallel R_2$  denotes the equivalent resistance of  $R_1$  and  $R_2$  connected in parallel.

- As  $\beta$ -value is fixed for a given transistor, this relation can be satisfied either by keeping  $R_E$  fairly large, or making  $R_1 || R_2$  very low.

- $_{\circ}$  If  $R_{E}$  is of large value, high  $V_{CC}$  is necessary. This increases cost as well as precautions necessary while handling.

- o If  $R_1 \parallel R_2$  is low, either  $R_1$  is low, or  $R_2$  is low, or both are low. A low  $R_1$  raises  $V_B$  closer to  $V_C$ , reducing the available swing in collector voltage, and limiting how large  $R_C$  can be made without driving the transistor out of active mode. A low  $R_2$  lowers  $V_{be}$ , reducing the allowed collector current. Lowering both resistor values draws more current from the power supply and lowers the input resistance of the amplifier as seen from the base.

- AC as well as DC feedback is caused by R<sub>E</sub>, which reduces the AC voltage gain of the amplifier. A method to avoid AC feedback while retaining DC feedback is discussed below.

# **Usage:**

The circuit's stability and merits as above make it widely used for linear circuits.

# Voltage divider with AC bypass capacitor

ᄆ

# Voltage divider with capacitor

The standard voltage divider circuit discussed above faces a drawback - AC feedback caused by resistor  $R_E$  reduces the gain. This can be avoided by placing a capacitor ( $C_E$ ) in parallel with  $R_E$ , as shown in circuit diagram.

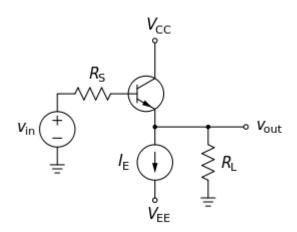

## **Emitter bias**

#### Emitter bias

When a split supply (dual power supply) is available, this biasing circuit is the most effective, and provides zero bias voltage at the emitter or collector for load. The negative supply  $V_{\rm EE}$  is used to forward-bias the emitter junction through  $R_{\rm E}$ . The positive supply  $V_{\rm CC}$  is used to reverse-bias the collector junction. Only two resistors are necessary for the common collector stage and four resistors for the common emitter or common base stage.

We know that,

$$V_B - V_E = V_{be}$$

If R<sub>B</sub> is small enough, base voltage will be approximately zero. Therefore emitter current is,

$$I_E = (V_{EE} - V_{be})/R_E$$

The operating point is independent of  $\beta$  if  $R_E >> R_B/\beta$

#### **Merit:**

Good stability of operating point similar to voltage divider bias.

#### **Demerit:**

This type can only be used when a split (dual) power supply is available.

# Class B and AB amplifiers

# Signal requirements

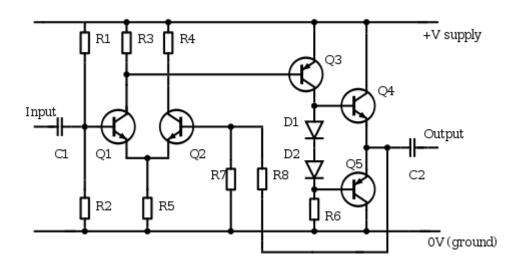

Class B and AB amplifiers employ 2 active devices to cover the complete 360 deg of input signal flow. Each transistor is therefore biased to perform over approximately 180 deg of the input signal. Class B bias is when the collector current  $I_c$  with no signal is just conducting (about 1% of maximum possible value). Class AB bias is

when the collector current  $I_c$  is about 1/4 of maximum possible value. The class AB push–pull output amplifier circuit below could be the basis for a moderate-power audio amplifier.

# A practical amplifier circuit

Q3 is a common emitter stage that provides amplification of the signal and the DC bias current through D1 and D2 to generate a bias voltage for the output devices. The output pair are arranged in Class AB push–pull, also called a complementary pair. The diodes D1 and D2 provide a small amount of constant voltage bias for the output pair, just biasing them into the conducting state so that crossover distortion is minimized. That is, the diodes push the output stage into class-AB mode (assuming that the base-emitter drop of the output transistors is reduced by heat dissipation).

This design automatically stabilizes its operating point, since overall feedback internally operates from DC up through the audio range and beyond. The use of fixed diode bias requires the diodes to be both electrically and thermally matched to the output transistors. If the output transistors conduct too much, they can easily overheat and destroy themselves, as the full current from the power supply is not limited at this stage.

A common solution to help stabilize the output device operating point is to include some emitter resistors, typically an ohm or so. Calculating the values of the circuit's resistors and capacitors is done

based on the components employed and the intended use of the amplifier.

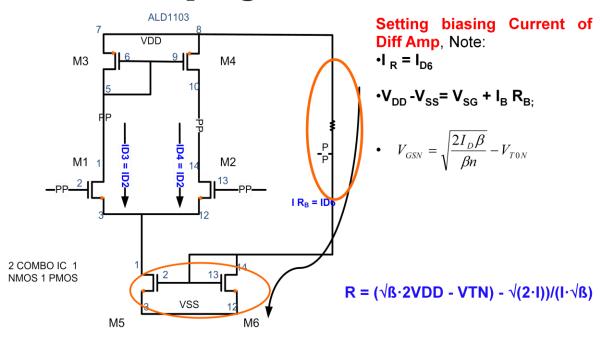

## Bias compensation

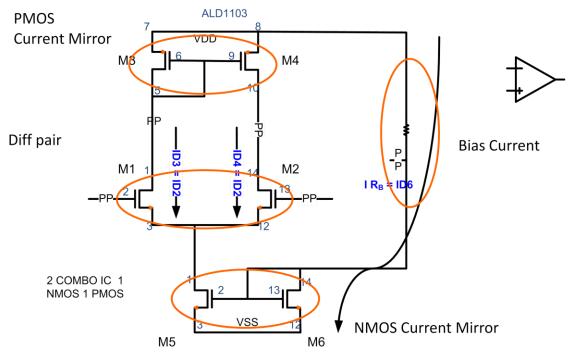

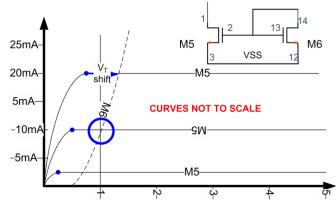

Temperature Compensation Of BJT Differential AmplifiersThe bipolar junction transistor (BJT) emitter-coupled differential-pair circuit is a familiar amplifier stage in the repertoire of analog designers, but has asurprising obscurity that needs to be revealed. This TechNote examines the emitter-circuit current source, I0, of BJT diff-amps and the effects on amplifier gain of different implementations for it. The widespread belief that a BJT current source can temperature-compensate the diff-amp is true, but the conditions for it do not appear to be widely known, based on most designs

## Thermal stability

**Thermal stability** is the stability of a molecule at high temperatures; i.e. a molecule with more stability has more resistance to decomposition at high temperatures.

**Thermal stability** also describes, as defined by Schmidt (1928), the stability of a water body and its resistance to mixing. This is the amount of work needed to transform the water body (e.g. a lake) to a uniform water density. The Schmidt stability 'S' is commonly measured in Joule per square meter or g\*cm/cm. Compare Stratification.

#### DESIGN FOR BIASING JFET

The **junction gate field-effect transistor** (**JFET** or **JUGFET**) is the simplest type of field-effect transistor. They are three-terminal semiconductor devices that can be used as electronically-controlled switches, amplifiers, or voltage-controlled resistors.

Unlike bipolar transistors, JFETs are exclusively voltage-controlled in that they do not need a biasing current. Electric charge flows through a semiconducting channel between source and drain terminals. By applying a reverse bias voltage to a gate terminal, the channel is "pinched", so that the electric current is impeded or switched off completely. A JFET is usually on when there is no potential difference between its gate and source terminals. If a potential difference of the proper polarity is applied between its gate and source terminals, the JFET will be more resistive to current flow, which means less current would flow in the channel between the source and drain terminals. Thus, JFETs are sometimes referred to as depletion-mode devices.

JFETs can have an n-type or p-type channel. In the n-type, if the voltage applied to the gate is less than that applied to the source, the current will be reduced (similarly in the p-type, if the voltage applied to the gate is greater than that applied to the source). A JFET has a large input impedance (sometimes on the order of  $10^{10}$  ohms), which means that it has a negligible effect on external components or circuits connected to its gate.

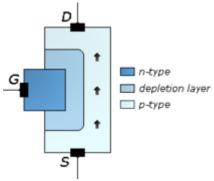

# Structure

ㅁ

Electric current from source to drain in a **p-channel JFET** is restricted when a voltage is applied to the gate.

The JFET is a long channel of semiconductor material, doped to contain an abundance of positive charge carriers or holes (p-type), or of negative carriers or electrons (n-type). Ohmic contacts at each end

form the source (S) and drain (D). A pn-junction is formed on one or both sides of the channel, or surrounding it, using a region with doping opposite to that of the channel, and biased using an ohmic gate contact (G).

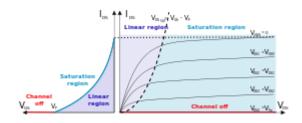

### **Function**

$\Box$

I-V characteristics and output plot of an n-channel JFET

JFET operation is like that of a garden hose. The flow of water through a hose can be controlled by squeezing it to reduce the cross section; the flow of electric charge through a JFET is controlled by constricting the current-carrying channel. The current also depends on the electric field between source and drain (analogous to the difference in pressure on either end of the hose).

Construction of the conducting channel is accomplished using the field effect: a voltage between the gate and source is applied to reverse bias the gate-source pn-junction, thereby widening the depletion layer of this junction (see top figure), encroaching upon the conducting channel and restricting its cross-sectional area. The depletion layer is so-called because it is depleted of mobile carriers and so is electrically non-conducting for practical purposes.<sup>[1]</sup>

When the depletion layer spans the width of the conduction channel, "pinch-off" is achieved and drain to source conduction stops. Pinch-off occurs at a particular reverse bias  $(V_{GS})$  of the gate-source junction. The pinch-off voltage  $(V_p)$  varies considerably, even among devices of the same type. For example,  $V_{GS(off)}$  for the Temic J202 device varies from -0.8 V to -4 V.<sup>[2]</sup> Typical values vary from -0.3 V to -10 V.

To switch off an **n**-channel device requires a **n**egative gate-source voltage  $(V_{GS})$ . Conversely, to switch off a **p**-channel device requires **p**ositive  $V_{GS}$ .

In normal operation, the electric field developed by the gate blocks source-drain conduction to some extent.

Some JFET devices are symmetrical with respect to the source and drain.

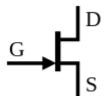

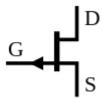

# **Schematic symbols**

$\Box$

Circuit symbol for an n-Channel JFET

ㅁ

Circuit symbol for a p-Channel JFET

The JFET gate is sometimes drawn in the middle of the channel (instead of at the drain or source electrode as in these examples). This symmetry suggests that "drain" and "source" are interchangeable, so the symbol should be used only for those JFETs where they are indeed interchangeable.

Officially, the style of the symbol should show the component inside a circle (representing the envelope of a discrete device). This is true in both the US and Europe. The symbol is usually drawn without the circle when drawing schematics of integrated circuits. More recently, the symbol is often drawn without its circle even for discrete devices.

In every case the arrow head shows the polarity of the P-N junction formed between the channel and gate. As with an ordinary diode, the arrow points from P to N, the direction of conventional current when forward-biased. An English mnemonic is that the arrow of an N-channel device "points in".

## **Comparison with other transistors**

At room temperature, JFET gate current (the reverse leakage of the gate-to-channel junction) is comparable to that of a MOSFET (which has insulating oxide between gate and channel), but much less than the base current of a bipolar junction transistor. The JFET has higher transconductance than the MOSFET, as well as lower flicker noise, and is therefore used in some low-noise, high input-impedance opamps.

### **History of the JFET**

The JFET was predicted by Julius Lilienfeld in 1925 and by the mid-1930s its theory of operation was sufficiently well known to justify a patent. However, it was not possible for many years to make doped crystals with enough precision to show the effect. In 1947, researchers John Bardeen, Walter Houser Brattain, and William Shockley were trying to make a JFET when they discovered the point-contact transistor. The first practical JFETs were made many years later, in spite of their conception long before the junction transistor. To some extent it can be treated as a hybrid of a MOSFET (metal–oxide–semiconductor field-effect transistor) and a BJT though an IGBT resembles more of the hybrid features.

### Mathematical model

The current in N-JFET due to a small voltage  $V_{DS}$  (that is, in the linear ohmic region) is given by treating the channel as a rectangular bar of material of electrical conductivity  $qN_d\mu_n$ :<sup>[3]</sup>

$$I_D = \frac{bW}{L} q N_d \mu_n V_{DS}$$

where

$I_D = drain-source$  current

b = channel thickness for a given gate voltage

W = channel width

L = channel length

$q = electron charge = 1.6 \times 10^{-19} C$

$\mu_n$  = electron mobility

$N_d = n$ -type doping (donor) concentration

The drain current in the saturation region is often approximated in terms of gate bias as:<sup>[3]</sup>

$$I_{DS} = I_{DSS} \left( 1 - \frac{V_{GS}}{V_P} \right)^2$$

where

$I_{DSS}$  is the saturation current at zero gate—source voltage.  $\cite{Continuous}$

In the saturation region, the JFET drain current is most significantly affected by the gate—source voltage and barely affected by the drain—source voltage.

If the channel doping is uniform, such that the depletion region thickness will grow in proportion to the square root of (the absolute value of) the gate—source voltage, then the channel thickness b can be expressed in terms of the zero-bias channel thickness a as: [citation needed]

$$b = a \left( 1 - \sqrt{\frac{V_{GS}}{V_P}} \right)$$

where

$V_P$  is the pinchoff voltage, the gate–source voltage at which the channel thickness goes to zero

a is the channel thickness at zero gate-source voltage.

Then the drain current in the linear ohmic region can be expressed as:

$$I_D = \frac{bW}{L} q N_d \mu_n V_{DS} = \frac{aW}{L} q N_d \mu_n \left( 1 - \sqrt{\frac{V_{GS}}{V_P}} \right) V_{DS}$$

or (in terms of  $I_{DSS}$ ): [citation needed]

$$I_D = \frac{2I_{DSS}}{V_P^2} \left(V_{GS} - V_P - \frac{V_{DS}}{2}\right) V_{DS} \label{eq:IDSS}$$

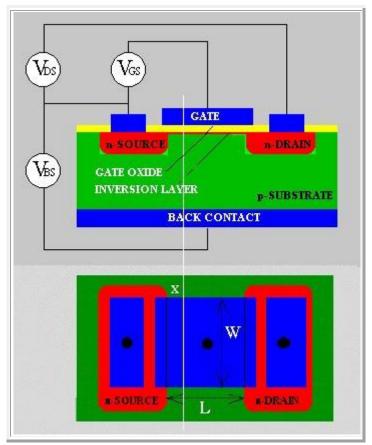

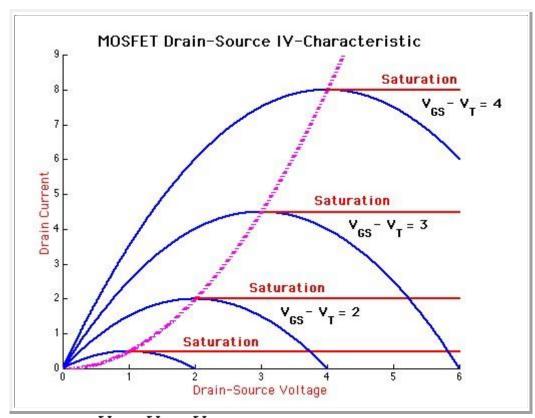

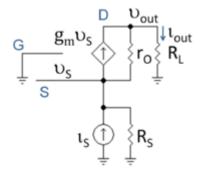

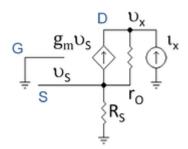

## **DESIGN OF BIASING MOSFET**

### **MOSFET**

From Wikipedia, the free encyclopedia

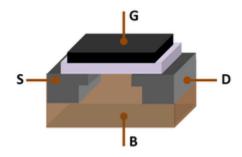

ᄆ

MOSFET showing gate (G), body (B), source (S) and drain (D) terminals. The gate is separated from the body by an insulating layer (white)

ㅁ

Two power MOSFETs in the surface-mount package D2PAK. Operating as switches, each of these components can sustain a blocking voltage of 120 volts in the OFF state, and can conduct a continuous current of 30 amperes in the ON state, dissipating up to about 100 watts and controlling a load of over 2000 watts. A matchstick is pictured for scale.

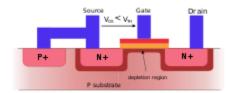

Ð

A cross section through an nMOSFET when the gate voltage  $V_{GS}$  is below the threshold for making a conductive channel; there is little or no conduction between the terminals drain and source; the switch is off. When the gate is more positive, it attracts electrons, inducing an n-type conductive channel in the substrate below the oxide, which allows electrons to flow between the n-doped terminals; the switch is on.

ㅁ

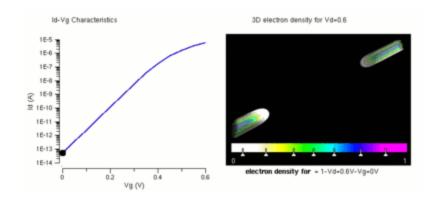

Simulation result for formation of inversion channel (electron density) and attainment of threshold voltage (IV) in a nanowire MOSFET. Note that the threshold voltage for this device lies around 0.45 V.

The metal—oxide—semiconductor field-effect transistor (MOSFET, MOS-FET, or MOS FET) is a type of transistor used for amplifying or switching electronic signals. Although the MOSFET is a four-terminal device with source (S), gate (G), drain (D), and body (B) terminals, the body (or substrate) of the MOSFET is often connected to the source terminal, making it a three-terminal device like other field-effect transistors. Because these two terminals are normally connected to each other (short-circuited) internally, only three terminals appear in electrical diagrams. The MOSFET is by far the most common transistor in both digital and analog circuits, though the bipolar junction transistor was at one time much more common.

In enhancement mode MOSFETs, a voltage drop across the oxide induces a conducting channel between the source and drain contacts via the field effect. The term "enhancement mode" refers to the increase of conductivity with increase in oxide field that adds carriers to the channel, also referred to as the inversion layer. The channel can contain electrons (called an nMOSFET or nMOS), or holes (called a pMOSFET or pMOS), opposite in type to the substrate, so nMOS is made with a p-type substrate, and pMOS with an n-type substrate (see article on semiconductor devices). In the less common depletion mode MOSFET, detailed later on, the channel consists of carriers in a surface impurity layer of opposite type to the substrate, and

conductivity is decreased by application of a field that depletes carriers from this surface layer. [2]

The "metal" in the name MOSFET is now often a misnomer because the previously metal gate material is now often a layer of polysilicon (polycrystalline silicon). Aluminium had been the gate material until the mid-1970s, when polysilicon became dominant, due to its capability to form self-aligned gates. Metallic gates are regaining popularity, since it is difficult to increase the speed of operation of transistors without metal gates.

Likewise, the "oxide" in the name can be a misnomer, as different dielectric materials are used with the aim of obtaining strong channels with smaller applied voltages.

An insulated-gate field-effect transistor or **IGFET** is a related term almost synonymous with MOSFET. The term may be more inclusive, since many "MOSFETs" use a gate that is not metal, and a gate insulator that is not oxide. Another synonym is MISFET for metal-insulator-semiconductor FET.

The basic principle of the field-effect transistor was first patented by Julius Edgar Lilienfeld in 1925.

# Composition

D

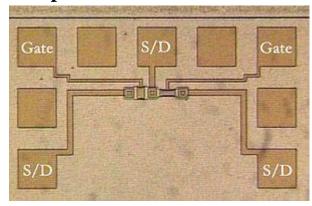

Photomicrograph of two metal-gate MOSFETs in a test pattern. Probe pads for two gates and three source/drain nodes are labeled.

Usually the semiconductor of choice is silicon, but some chip manufacturers, most notably IBM and Intel, recently started using a chemical compound of silicon and germanium (SiGe) in MOSFET channels. Unfortunately, many semiconductors with better electrical properties than silicon, such as gallium arsenide, do not form good semiconductor-to-insulator interfaces, thus are not suitable for MOSFETs. Research continues on creating insulators with acceptable electrical characteristics on other semiconductor material.

In order to overcome the increase in power consumption due to gate current leakage, a high-κ dielectric is used instead of silicon dioxide for the gate insulator, while polysilicon is replaced by metal gates (see Intel announcement<sup>[3]</sup>).

The gate is separated from the channel by a thin insulating layer, traditionally of silicon dioxide and later of silicon oxynitride. Some companies have started to introduce a high-κ dielectric + metal gate combination in the 45 nanometer node.

When a voltage is applied between the gate and body terminals, the electric field generated penetrates through the oxide and creates an "inversion layer" or "channel" at the semiconductor-insulator interface. The inversion channel is of the same type, p-type or n-type, as the source and drain, thus it provides a channel through which current can pass. Varying the voltage between the gate and body modulates the conductivity of this layer and thereby controls the current flow between drain and source.

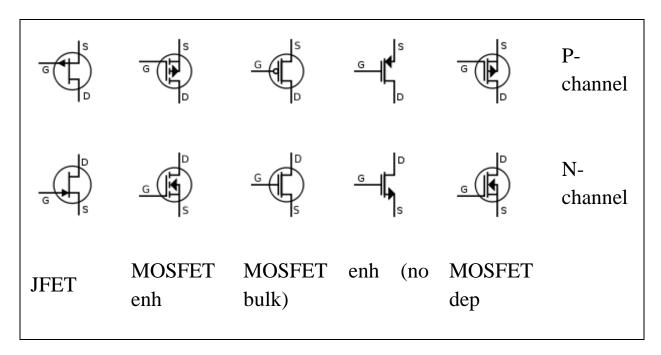

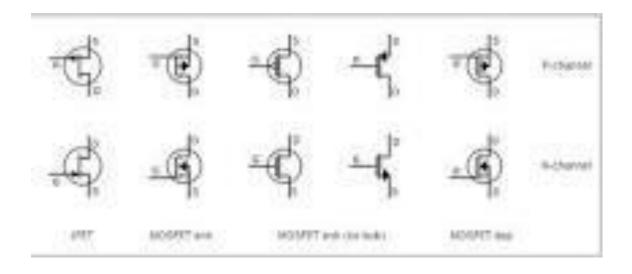

# **Circuit symbols**

A variety of symbols are used for the MOSFET. The basic design is generally a line for the channel with the source and drain leaving it at right angles and then bending back at right angles into the same direction as the channel. Sometimes three line segments are used for enhancement mode and a solid line for depletion mode. (see Depletion and enhancement modes) Another line is drawn parallel to the channel for the gate.

The "bulk" or "body" connection, if shown, is shown connected to the back of the channel with an arrow indicating PMOS or NMOS. Arrows always point from P to N, so an NMOS (N-channel in P-well or P-substrate) has the arrow pointing in (from the bulk to the channel). If the bulk is connected to the source (as is generally the case with discrete devices) it is sometimes angled to meet up with the source leaving the transistor. If the bulk is not shown (as is often the case in IC design as they are generally common bulk) an inversion symbol is sometimes used to indicate PMOS, alternatively an arrow on the source may be used in the same way as for bipolar transistors (out for nMOS, in for pMOS).

Comparison of enhancement-mode and depletion-mode MOSFET symbols, along with JFET symbols. The orientation of the symbols, (most significantly the position of source relative to drain) is such that more positive voltages appear higher on the page than less positive voltages, implying current flowing "down" the page: [4][5][6]

In schematics where G, S, D are not labeled, the detailed features of the symbol indicate which terminal is source and which is drain. For enhancement-mode and depletion-mode MOSFET symbols (in columns two and five), the source terminal is the one connected to the triangle. Additionally, in this diagram, the gate is shown as an "L" shape, whose input leg is closer to S than D, also indicating which is

which. However, these symbols are often drawn with a "T" shaped gate (as elsewhere on this page), so it is the triangle which must be relied upon to indicate the source terminal.

For the symbols in which the bulk, or body, terminal is shown, it is here shown internally connected to the source (i.e., the black triangles in the diagrams in columns 2 and 5). This is a typical configuration, but by no means the only important configuration. In general, the MOSFET is a four-terminal device, and in integrated circuits many of the MOSFETs share a body connection, not necessarily connected to the source terminals of all the transistors.

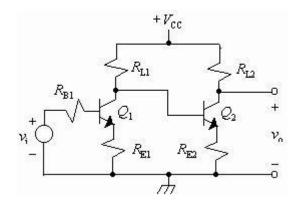

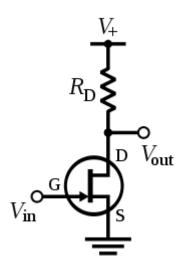

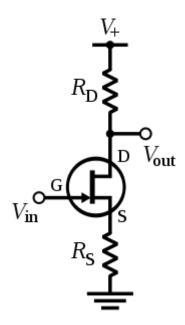

### **UNIT-2 BJT AMPLIFIERS**

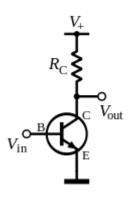

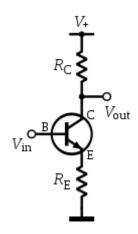

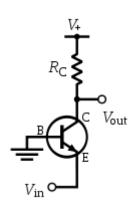

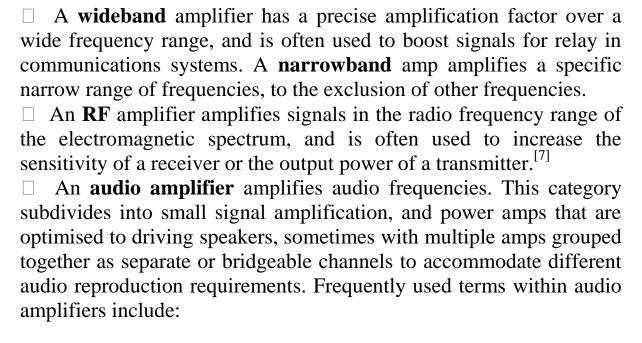

In electronics, a **common emitter** amplifier is one of three basic single-stage bipolar-junction-transistor (BJT) amplifier topologies, typically used as a voltage amplifier.

In this circuit the base terminal of the transistor serves as the input, the collector is the output, and the emitter is common to both (for example, it may be tied to ground reference or a power supply rail), hence its name. The analogous field-effect transistor circuit is the common source amplifier, and the analogous tube circuit is the common cathode amplifier.

# **Emitter degeneration**

Figure 2: Adding an emitter resistor decreases gain, but increases linearity and stability

Common emitter amplifiers give the amplifier an inverted output and can have a very high gain that may vary widely from one transistor to the next. The gain is a strong function of both temperature and bias current, and so the actual gain is somewhat unpredictable. Stability is another problem associated with such high gain circuits due to any unintentional positive feedback that may be present.

Other problems associated with the circuit are the low input dynamic range imposed by the small-signal limit; there is high distortion if this limit is exceeded and the transistor ceases to behave like its small-signal model. One common way of alleviating these issues is with the use of negative feedback, which is usually implemented with emitter degeneration. Emitter degeneration refers to the addition of a small resistor (or any impedance) between the emitter and the common signal source (e.g., the ground reference or a power supply rail). This impedance  $R_{\rm E}$  reduces the overall transconductance  $G_m = g_m$  of the circuit by a factor of  $g_m R_{\rm E} + 1$ , which makes the voltage gain

$$A_{\rm v} \triangleq \frac{v_{\rm out}}{v_{\rm in}} = \frac{-g_m R_{\rm C}}{g_m R_{\rm E} + 1} \approx -\frac{R_{\rm C}}{R_{\rm E}}$$

(where  $g_m R_{\rm E} \gg 1$ ).

So the voltage gain depends almost exclusively on the ratio of the resistors  $R_{\rm C}/R_{\rm E}$  rather than the transistor's intrinsic and unpredictable characteristics. The distortion and stability characteristics of the circuit are thus improved at the expense of a reduction in gain.

#### **Characteristics**

At low frequencies and using a simplified hybrid-pi model, the following small-signal characteristics can be derived.

Definition Expression (with Expression emitter degeneration) (without emitter degeneration, i.e.,

$$\mathbf{R_E} = \mathbf{0})$$

$$\mathbf{Current}$$

$$\mathbf{gain}$$

$$A_{\mathbf{i}} \triangleq \frac{i_{\mathrm{out}}}{i_{\mathrm{in}}}$$

$$\beta$$

$$\mathbf{Voltage}$$

$$\mathbf{gain}$$

$$A_{\mathbf{v}} \triangleq \frac{v_{\mathrm{out}}}{v_{\mathrm{in}}}$$

$$-\frac{\beta R_{\mathrm{C}}}{r_{\pi} + (\beta + 1)R_{\mathrm{E}}}$$

$$\approx -g_m R_{\mathrm{C}}$$

$$\mathbf{Input}$$

$$\mathbf{impedance}$$

$$r_{\mathrm{in}} \triangleq \frac{v_{\mathrm{in}}}{i_{\mathrm{in}}}$$

$$r_{\pi} + (\beta + 1)R_{\mathrm{E}}$$

$$r_{\pi}$$

$$\mathbf{Output}$$

$$\mathbf{impedance}$$

$$r_{\mathrm{out}} \triangleq \frac{v_{\mathrm{out}}}{i_{\mathrm{out}}}$$

$$R_{\mathrm{C}}$$

If the emitter degeneration resistor is not present, then  $R_{\rm E}=0\,\Omega$ , and the expressions effectively simplify to the ones given by the rightmost column (note that the voltage gain is an ideal value; the actual gain is somewhat unpredictable). As expected, when  $R_{\rm E}$  is increased, the input impedance is increased and the voltage gain  $A_{\rm v}$  is reduced.

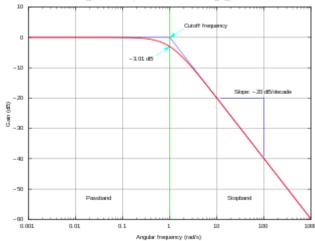

#### **Bandwidth**

The bandwidth of the common-emitter amplifier tends to be low due to high capacitance resulting from the Miller effect. The parasitic base-collector capacitance  $C_{\text{CB}}$  appears like a larger parasitic capacitor  $C_{\text{CB}}(1-A_{\text{v}})$  (where  $A_{\text{v}}$  is negative) from the base to ground. This large capacitor greatly decreases the bandwidth of the amplifier as it makes the time constant of the parasitic input RC filter  $r_{\text{s}}(1-A_{\text{V}})C_{\text{CB}}$  where  $r_{\text{s}}$  is the output impedance of the signal source connected to the ideal base.

The problem can be mitigated in several ways, including:

• Reduction of the voltage gain magnitude  $|A_v|$  (e.g., by using emitter degeneration).

- Reduction of the output impedance  $r_s$  of the signal source connected to the base (e.g., by using an emitter follower or some other voltage follower).

- Using a cascode configuration, which inserts a low input impedance current buffer (e.g. a common base amplifier) between the transistor's collector and the load. This configuration holds the transistor's collector voltage roughly constant, thus making the base to collector gain zero and hence (ideally) removing the Miller effect.

- Using a differential amplifier topology like an emitter follower driving a grounded-base amplifier; as long as the emitter follower is truly a common-collector amplifier, the Miller effect is removed.

The Miller effect negatively affects the performance of the common source amplifier in the same way (and has similar solutions). When an AC signal is applied to the transistor amplifier it causes the base voltage VB to fluctuate in value at the AC signal. The positive half of the applied signal will cause an increase in the value of VB this turn will increase the base current IB and cause a corresponding increase in emitter current IE and collector current IC. As a result, the collector emitter voltage will be reduced because of the increase voltage drop across RL. The negative alternation of an AC signal will cause a decrease in IB this action then causes a corresponding decrease in IE through RL. The output signal of a common- emitter amplifier is therefore 180 degrees out of phase with the input signal.

It is also named common- emitter amplifier because the emitter of the transistor is common to both the input circuit and output circuit. The input signal is applied across the ground and the base circuit of the transistor. The output signal appears across ground and the collector of the transistor. Since the emitter is connected to the ground, it is common to signals, input and output.

The common- emitter circuit is the most widely used of junction, transistor amplifiers. As compared with the common- base connection, it has higher input impedance and lower output impedance. A single power supply is easily used for biasing. In

addition, higher voltage and power gains are usually obtained for common-emitter (CE) operation.

Current gain in the common emitter circuit is obtained from the base and the collector circuit currents. Because a very small change in base current produces a large change in collector current, the current gain  $(\beta)$  is always greater than unity for the common-emitter circuit, a typical value is about 50.

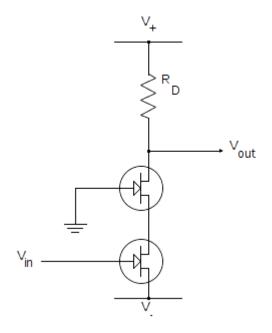

### SMALL SIGNAL ANALYSIS OF CC AMP

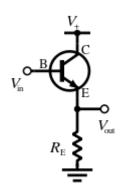

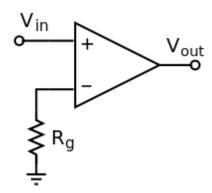

In electronics, a **common collector** amplifier (also known as an **emitter follower**) is one of three basic single-stage bipolar junction transistor (BJT) amplifier topologies, typically used as a voltage buffer.

In this circuit the base terminal of the transistor serves as the input, the emitter is the output, and the collector is common to both (for example, it may be tied to ground reference or a power supply rail), hence its name. The analogous field-effect transistor circuit is the common drain amplifier

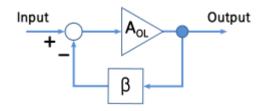

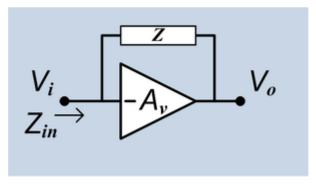

### **Basic circuit**

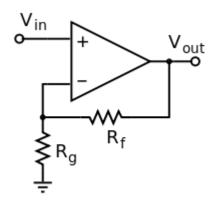

Figure 2: A negative feedback amplifier

The circuit can be explained by viewing the transistor as being under the control of negative feedback. From this viewpoint, a common collector stage (Fig. 1) is an amplifier with full series negative feedback. In this configuration (Fig. 2 with  $\beta$  = 1), the entire output voltage  $V_{OUT}$  is placed contrary and in series with the input voltage  $V_{IN}$ . Thus the two voltages are subtracted according to KVL (the subtractor from the function block diagram is implemented just by the input loop) and their difference Vdiff =  $V_{IN}$  -  $V_{OUT}$  is applied to the base-emitter junction. The transistor monitors continuously Vdiff and adjusts its emitter voltage almost equal (less  $V_{BEO}$ ) to the input voltage by passing the according collector current through the emitter resistor  $R_E$ . As a result, the output voltage follows the input voltage variations from  $V_{BEO}$  up to  $V_+$ ; hence the name, emitter follower.

Intuitively, this behavior can be also understood by realizing that the base-emitter voltage in the bipolar transistor is very insensitive to bias changes, so any change in base voltage is transmitted (to good approximation) directly to the emitter. It depends slightly on various disturbances (transistor tolerances, temperature variations, load resistance, collector resistor if it is added, etc.) since the transistor reacts to these disturbances and restores the equilibrium. It never saturates even if the input voltage reaches the positive rail.

The common collector circuit can be shown mathematically to have a voltage gain of almost unity:

$$A_{\rm v} = \frac{v_{\rm out}}{v_{\rm in}} \approx 1$$

Figure 3: PNP version of the emitter follower circuit, all polarities are reversed.

A small voltage change on the input terminal will be replicated at the output (depending slightly on the transistor's gain and the value of the load resistance; see gain formula below). This circuit is useful because it has a large input impedance, so it will not load down the previous circuit:

$$r_{\rm in} \approx \beta_0 R_{\rm E}$$

and a small output impedance, so it can drive low-resistance loads:

$$r_{

m out} pprox R_{

m E} \| rac{R_{

m source}}{eta_0}$$

Typically, the emitter resistor is significantly larger and can be removed from the equation:

$$r_{\rm out} \approx \frac{R_{\rm source}}{\beta_0}$$

# **Applications**

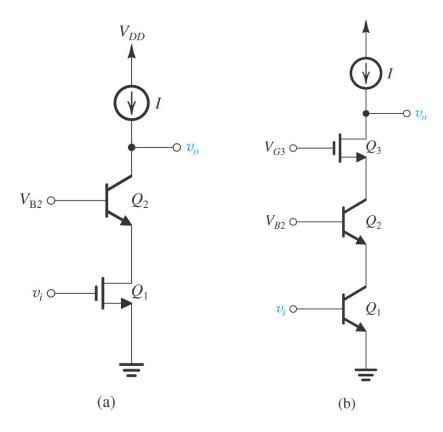

ㅁ

Figure 4: NPN voltage follower with current source biasing suitable for integrated circuits

The low output impedance allows a source with a large output impedance to drive a small load impedance; it functions as a voltage buffer. In other words, the circuit has current gain (which depends largely on the  $h_{FE}$  of the transistor) instead of voltage gain. A small change to the input current results in much larger change in the output current supplied to the output load.

One aspect of buffer action is transformation of impedances. For example, the Thévenin resistance of a combination of a voltage follower driven by a voltage source with high Thévenin resistance is reduced to only the output resistance of the voltage follower (a small resistance). That resistance reduction makes the combination a more ideal voltage source. Conversely, a voltage follower inserted between a small load resistance and a driving stage presents a large load to the driving stage—an advantage in coupling a voltage signal to a small load.

This configuration is commonly used in the output stages of class-B and class-AB amplifiers. The base circuit is modified to operate the transistor in class-B or AB mode. In class-A mode, sometimes an active current source is used instead of  $R_E$  (Fig. 4) to improve linearity and/or efficiency.<sup>[1]</sup>

#### Characteristics

At low frequencies and using a simplified hybrid-pi model, the following small-signal characteristics can be derived. (Parameter  $\beta = g_m r_{\pi}$  and the parallel lines indicate components in parallel.)

|                 | Definiti<br>on Expression                                                            | Approxima<br>te<br>expression | Conditions            |

|-----------------|--------------------------------------------------------------------------------------|-------------------------------|-----------------------|

| Current<br>gain | $A_{ m i} = rac{i_{ m out}}{i_{ m in}} eta_0 + 1$                                   | $\approx \beta_0$             | $\beta_0 \gg 1$       |

| Voltage         | $A_{\rm v} = \frac{v_{\rm out}}{v_{\rm in}} \frac{g_m R_{\rm E}}{g_m R_{\rm E} + 1}$ | ≈ 1                           | $g_m R_{\rm E} \gg 1$ |

# gain

Input resistan

$$r_{\rm in}=\frac{v_{\rm in}}{i_{\rm in}}\;r_\pi+(\beta_0+1)R_{\rm E}\;pprox \beta_0R_{\rm E} \qquad (g_mR_{\rm E}\gg 1)\wedge(\beta_0\gg ce$$

$$\begin{array}{l} \textbf{Output} \\ \textbf{resistan} \ \ r_{\text{out}} = \frac{v_{\text{ol}}}{i_{\text{ol}}} R_{\text{E}} \parallel \left( \frac{r_{\pi} + R_{\text{sout}}}{\beta_0 + 1} \approx \frac{1}{g_m} + \frac{R_{\text{sou}}}{\beta_0} (\beta_0 \gg 1) \wedge (r_{\text{in}} \gg R_{\text{so}} + \frac{1}{g_m}) \right) \\ \textbf{ce} \end{array}$$

Where  $R_{\text{source}}$  is the Thévenin equivalent source resistance.

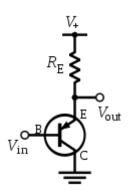

### SMALL SIGNAL ANALYSIS OF CB AMP

In electronics, a **common base** (also known as **grounded-base**) amplifier is one of three basic single-stage bipolar junction transistor (BJT) amplifier topologies, typically used as a current buffer or voltage amplifier.

In this circuit the emitter terminal of the transistor serves as the input, the collector the output, and the base is connected to ground, or "common", hence its name. The analogous field-effect transistor circuit is the common gate amplifier

# **Simplified Operation**

As current is sunk from the emitter this provides potential difference so causing the transistor to conduct.<sup>[1]</sup> The current conducted via the collector is proportional to the voltage across the base-emitter junction, accounting for the bias, as with other configurations.<sup>[2]</sup>

Therefore, if no current is sunk at the emitter the transistor does not conduct.

# **Applications**

This arrangement is not very common in low-frequency circuits, where it is usually employed for amplifiers that require an unusually low input impedance, for example to act as a preamplifier for moving-coil microphones. However, it is popular in high-frequency amplifiers, for example for VHF and UHF, because its input capacitance does not suffer from the Miller effect, which degrades the bandwidth of the common emitter configuration, and because of the relatively high isolation between the input and output. This high isolation means that there is little feedback from the output back to the input, leading to high stability.

This configuration is also useful as a current buffer since it has a current gain of approximately unity (see formulas below). Often a common base is used in this manner, preceded by a common emitter stage. The combination of these two form the cascode configuration, which possesses several of the benefits of each configuration, such as high input impedance and isolation.

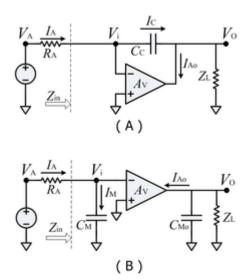

# Low-frequency characteristics

At low frequencies and under small-signal conditions, the circuit in Figure 1 can be represented by that in Figure 2, where the hybrid-pi model for the BJT has been employed. The input signal is represented by a Thévenin voltage source,  $v_s$ , with a series resistance  $R_s$  and the load is a resistor  $R_L$ . This circuit can be used to derive the following characteristics of the common base amplifier.

|                                | Definitio<br>Expression                                                                                 | Approximate expression                     | Conditions                    |

|--------------------------------|---------------------------------------------------------------------------------------------------------|--------------------------------------------|-------------------------------|

| Open - circui t voltag e gain  | ,                                                                                                       | $g_m R_C$                                  | $r_O \gg R_C$                 |

| Short - circui t curre nt gain |                                                                                                         | 1                                          | $\beta\gg 1$                  |

| Input<br>resist<br>ance        | $R_{\rm in} = \frac{v_i}{i_i}  \frac{(r_O + R_C    R_L) r_E}{r_O + r_E + \frac{R_C    R_L}{\beta + 1}}$ | $r_E \left( \approx \frac{1}{g_m} \right)$ | $r_O \gg R_C   R_L$           |

| Outp<br>ut<br>resist<br>ance   | $R_{\text{out}} = \frac{v_o}{-i} R_C \  \{ [1 + g_m(r_\pi \  R_S)] \} \ $                               | $R_C    r_O$ $R_C    [(r_\pi    R_S)]$     | $R_S \ll r_E$ 1 $R_S \gg r_E$ |

**Note:** Parallel lines (||) indicate components in parallel.

In general the overall voltage/current gain may be substantially less than the open/short circuit gains listed above (depending on the source and load resistances) due to the loading effect.

### **Active loads**

For voltage amplification, the range of allowed output voltage swing in this amplifier is tied to its voltage gain when a resistor load R<sub>C</sub> is employed, as in Figure 1. That is, large voltage gain requires large R<sub>C</sub>, and that in turn implies a large DC voltage drop across R<sub>C</sub>. For a given supply voltage, the larger this drop, the smaller the transistor V<sub>CB</sub> and the less output swing is allowed before saturation of the transistor occurs, with resultant distortion of the output signal. To avoid this situation, an active load can be used, for example, a current mirror. If this choice is made, the value of R<sub>C</sub> in the table above is replaced by the small-signal output resistance of the active load, which is generally at least as large as the r<sub>O</sub> of the active transistor in Figure 1. On the other hand, the DC voltage drop across the active load is a fixed low value (the **compliance voltage** of the active load), much less than the DC voltage drop incurred for comparable gain using a resistor R<sub>C</sub>. That is, an active load imposes less restriction on the output voltage swing. Notice that active load or not, large AC gain still is coupled to large AC output resistance, which leads to poor voltage division at the output except for large loads  $R_L >> R_{out}$ .

For use as a current buffer, gain is not affected by  $R_C$ , but output resistance is. Because of the current division at the output, it is desirable to have an output resistance for the buffer much larger than the load  $R_L$  being driven so large signal currents can be delivered to a load. If a resistor  $R_C$  is used, as in Figure 1, a large output resistance is coupled to a large  $R_C$ , again limiting the signal swing at the output. (Even though current is delivered to the load, usually a large current signal into the load implies a large voltage swing across the load as well.) An active load provides high AC output resistance with much less serious impact upon the amplitude of output signal swing.

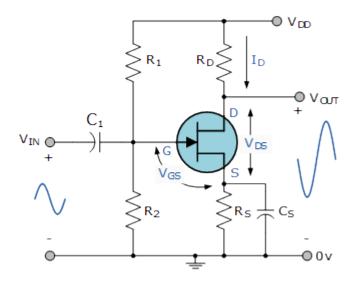

### AC LOADLINE

Semiconductor circuits typically have both DC and AC currents in them, with a source of DC current to bias the nonlinear semiconductor to the correct operating point, and the AC signal superimposed on the DC. Load lines can be used separately for both DC and AC analysis. The DC load line is the load line of the DC equivalent circuit, defined by reducing the reactive components to zero (replacing capacitors by

open circuits and inductors by closed circuits). It is used to determine the correct DC operating point, often called the Q point.

Once a DC operating point is defined by the DC load line, an AC load line can be drawn through the Q point. The AC load line is a straight line with a slope equal to the AC impedance facing the nonlinear device, which is in general different from the DC resistance. The ratio of AC voltage to current in the device is defined by this line. Because the impedance of the reactive components will vary with frequency, the slope of the AC load line depends on the frequency of the applied signal. So there are many AC load lines, that vary from the DC load line (at low frequency) to a limiting AC load line, all having a common intersection at the dc operating point. This limiting load line, generally referred to as the AC load line, is the load line of the circuit at "infinite frequency", and can be found by replacing capacitors with short circuits, and inductors with open circuits.

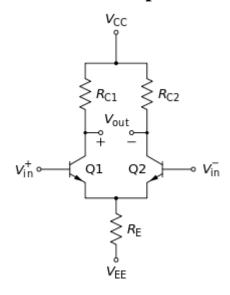

#### DIFFERENTIAL AMP

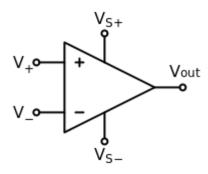

A **differential amplifier** is a type of electronic amplifier that amplifies the difference between two voltages but does not amplify the particular voltages.

# **Theory**

Many electronic devices use differential amplifiers internally. The output of an ideal differential amplifier is given by:

$$V_{\text{out}} = A_{\text{d}}(V_{\text{in}}^+ - V_{\text{in}}^-)$$

Where  $V_{\rm in}^+$  and  $V_{\rm in}^-$  are the input voltages and  $A_{\rm d}$  is the differential gain. In practice, however, the gain is not quite equal for the two inputs. This means, for instance, that if  $V_{\rm in}^+$  and  $V_{\rm in}^-$  are equal, the output will not be zero, as it would be in the ideal case. A more realistic expression for the output of a differential amplifier thus includes a second term.

$$V_{\text{out}} = A_{\text{d}}(V_{\text{in}}^{+} - V_{\text{in}}^{-}) + A_{\text{c}}\left(\frac{V_{\text{in}}^{+} + V_{\text{in}}^{-}}{2}\right)$$

$A_{cis}$  called the common-mode gain of the amplifier. As differential amplifiers are often used to null out noise or biasvoltages that appear at both inputs, a low common-mode gain is usually desired.

The common-mode rejection ratio (CMRR), usually defined as the ratio between differential-mode gain and common-mode gain, indicates the ability of the amplifier to accurately cancel voltages that are common to both inputs. The common-mode rejection ratio is defined as:

$$\text{CMRR} = 10 \log_{10} \left( \frac{A_{\text{d}}}{A_{\text{c}}} \right)^2 = 20 \log_{10} \left( \frac{A_{\text{d}}}{|A_{\text{c}}|} \right)$$

In a perfectly symmetrical differential amplifier,  $A_c$  is zero and the CMRR is infinite. Note that a differential amplifier is a more general form of amplifier than one with a single input; by grounding one input of a differential amplifier, a single-ended amplifier results.

# Long-tailed pair

# Historical background

Differential amplifiers are usually implemented with a basic circuit called long-tailed pair. This circuit was originally implemented using a pair of vacuum tubes. The circuit works the same way for all three-terminal devices with current gain. The long-tail resistor circuit bias points are largely determined by Ohm's Law and less so by active component characteristics.

The long-tailed pair was developed from earlier knowledge of push-pull circuit techniques and measurement bridges. An early circuit which closely resembles a long-tailed pair was published by Matthews in 1934, and it seems likely that this was intended to be a true long-tailed pair but was published with a drawing error. The earliest definite long-tailed pair circuit appears in a patent submitted by Alan Blumlein in 1936. By the end of the 1930s the topology was well established and had been described by various authors including Offner (1937), Schmitt (1937) and Toennies (1938) and it was particularly used for detection and measurement of physiological impulses.

The long-tailed pair was very successfully used in early British computing, most notably the Pilot ACE model and descendants, [nb 1] Wilkes' EDSAC, and probably others designed by people who worked with Blumlein or his peers. The long-tailed pair has many attributes as a switch: largely immune to tube (transistor) variations (of great importance when machines contained 1,000 or more tubes), high gain, gain stability, high input impedance, medium/low output impedance, good clipper (with not-too-long tail), non-inverting (EDSAC contained no inverters!) and large output voltage swings. One disadvantage is that the output voltage swing (typically ±10–20 V)

was imposed upon a high DC voltage (200 V or so), requiring care in signal coupling, usually some form of wide-band DC coupling. Many computers of this time tried to avoid this problem by using only AC-coupled pulse logic, which made them very large and overly complex (ENIAC: 18,000 tubes for a 20 digit calculator) or unreliable. DC-coupled circuitry became the norm after the first generation of vacuum tube computers.

### **Configurations**

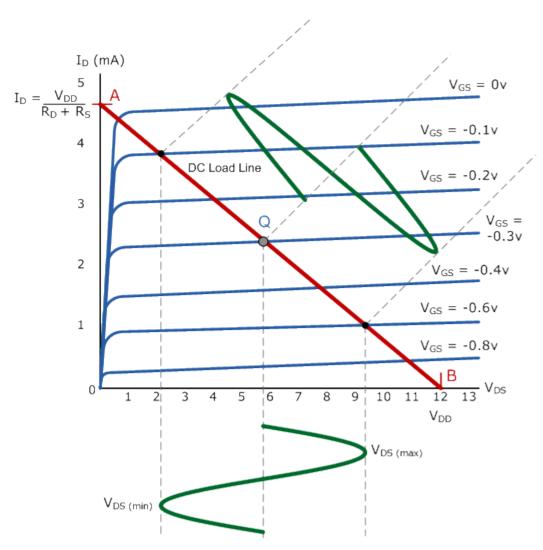

A differential (long-tailed, [nb 2] emitter-coupled) pair amplifier consists of two amplifying stages with common (emitter, source or cathode) degeneration.

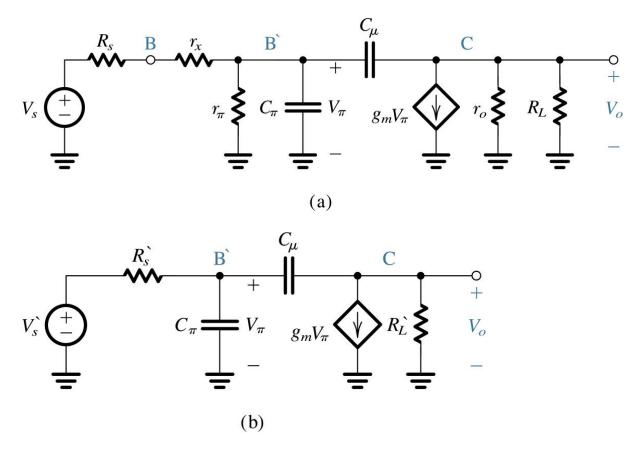

# **Differential output**

ㅁ

Figure 2: A classic long-tailed pair

With two inputs and two outputs, this forms a differential amplifier stage (Fig. 2). The two bases (or grids or gates) are inputs which are differentially amplified (subtracted and multiplied) by the pair; they can be fed with a differential (balanced) input signal, or one input could be grounded to form a phase splitter circuit. An amplifier with differential output can drive floating load or another stage with differential input.

### Single-ended output

If the differential output is not desired, then only one output can be used (taken from just one of the collectors (or anodes or drains), disregarding the other output without a collector inductor; this configuration is referred to as single-ended output. The gain is half that of the stage with differential output. To avoid sacrificing gain, a differential to single-ended converter can be utilized. This is often implemented as a current mirror (Fig. 3).

## **Operation**

To explain the circuit operation, four particular modes are isolated below although, in practice, some of them act simultaneously and their effects are superimposed.

## **Biasing**

In contrast with classic amplifying stages that are biased from the side of the base (and so they are highly  $\beta$ -dependent), the differential pair is directly biased from the side of the emitters by sinking/injecting the total quiescent current. The series negative feedback (the emitter degeneration) makes the transistors act as voltage stabilizers; it forces them to adjust their  $V_{BE}$  voltages (base currents) to pass the quiescent current through their collector-emitter junctions. [nb 3] So, due to the negative feedback, the quiescent current depends slightly on the transistor's  $\beta$ .

The biasing base currents needed to evoke the quiescent collector currents usually come from the ground, pass through the input sources and enter the bases. So, the sources have to be galvanic (DC) to ensure paths for the biasing currents and low resistive enough to not create significant voltage drops across them. Otherwise, additional DC elements should be connected between the bases and the ground (or the positive power supply).

### Common mode

At common mode (the two input voltages change in the same directions), the two voltage (emitter) followers cooperate with each other working together on the common high-resistive emitter load (the "long tail"). They all together increase or decrease the voltage of the common emitter point (figuratively speaking, they together "pull up" or "pull down" it so that it moves). In addition, the dynamic load "helps" them by changing its instant ohmic resistance in the same direction as the input voltages (it increases when the voltage increases and vice versa.) thus keeping up constant total resistance between the two supply rails. There is a full (100%) negative feedback; the two input base voltages and the emitter voltage change simultaneously while the collector currents and the total current do not change. As a result, the output collector voltages do not change as well.

### **Differential mode**

Normal. At differential mode (the two input voltages change in opposite directions), the two voltage (emitter) followers oppose each other - while one of them tries to increase the voltage of the common emitter point, the other tries to decrease it (figuratively speaking, one of them "pulls up" the common point while the other "pulls down" it so that it stays immovable) and v.v. So, the common point does not change its voltage; it behaves like a virtual ground with a magnitude determined by the common-mode input voltages. The high-resistive emitter element does not play any role since it is shunted by the other low-resistive emitter follower. There is no negative feedback since the emitter voltage does not change at all when the input base voltages change. The common quiescent current vigorously steers between the two transistors and the output collector voltages vigorously change. The two transistors mutually ground their emitters; so, although they are common-collector stages, they actually act as common-emitter stages with maximum gain. Bias stability and independence from variations in device parameters can be improved by negative feedback introduced via cathode/emitter resistors with relatively resistances.

**Overdriven.** If the input differential voltage changes significantly (more than about a hundred millivolts), the base-emitter junction of the transistor driven by the lower input voltage becomes backward biased and its collector voltage reaches the positive supply rail. The other transistor (driven by the higher input voltage) saturates and its collector voltage begins following the input one. This mode is used in differential switches and ECL gates.

**Breakdown.** If the input voltage continues increasing and exceeds the base-emitter breakdown voltage, the base-emitter junction of the transistor driven by the lower input voltage breaks down. If the input sources are low resistive, an unlimited current will flow directly through the "diode bridge" between the two input sources and will damage them.

At common mode, the emitter voltage follows the input voltage variations; there is a full negative feedback and the gain is minimum. At differential mode, the emitter voltage is fixed (equal to the instant common input voltage); there is no negative feedback and the gain is maximum.

#### **CMRR**

The **common-mode rejection ratio** (CMRR) of a differential amplifier (or other device) is the rejection by the device of unwanted input signals common to both input leads, relative to the wanted difference signal. An ideal differential amplifier would have infinite CMRR; this is not achievable in practice. A high CMRR is required when a differential signal must be amplified in the presence of a possibly large common-mode input. An example is audio transmission over balanced lines.

# **Theory**

Ideally, a differential amplifier takes the voltages,  $V_+$  and  $V_-$  on its two inputs and produces an output voltage  $V_o = A_d(V_+ - V_-)$ , where  $A_d$  is the differential gain. However, the output of a real differential amplifier is better described as

$$V_{\rm o} = A_{\rm d}(V_+ - V_-) + \frac{1}{2}A_{\rm cm}(V_+ + V_-),$$

where  $A_{cm}$  is the common-mode gain, which is typically much smaller than the differential gain.

The CMRR is defined as the ratio of the powers of the differential gain over the common-mode gain, measured in positive decibels (thus using the 20 log rule):

$$\mathrm{CMRR} = \left(\frac{A_{\mathrm{d}}}{|A_{\mathrm{cm}}|}\right) = 10\log_{10}\left(\frac{A_{\mathrm{d}}}{A_{\mathrm{cm}}}\right)^2 dB = 20\log_{10}\left(\frac{A_{\mathrm{d}}}{|A_{\mathrm{cm}}|}\right) dB$$

As differential gain should exceed common-mode gain, this will be a positive number, and the higher the better.

The CMRR is a very important specification, as it indicates how much of the common-mode signal will appear in your measurement. The value of the CMRR often depends on signal frequency as well, and must be specified as a function thereof.

It is often important in reducing noise on transmission lines. For example, when measuring the resistance of a thermocouple in a noisy environment, the noise from the environment appears as an offset on both input leads, making it a common-mode voltage signal. The CMRR of the measurement instrument determines the attenuation applied to the offset or noise.

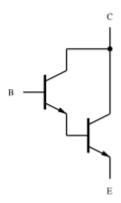

### DARLINGTON AMPLIFIER

pair) is a compound structure consisting of two bipolar transistors (either integrated or separated devices) connected in such a way that the current amplified by the first transistor is amplified further by the second one. This configuration gives a much higher common/emitter current gain than each transistor taken separately and, in the case of integrated devices, can take less space than two individual transistors because they can use a shared collector. Integrated Darlington pairs come packaged singly in transistor-like

packages or as an array of devices (usually eight) in an integrated circuit.

The Darlington configuration was invented by Bell Laboratories engineer Sidney Darlington in 1953. He patented the idea of having two or three transistors on a single chip sharing a collector.<sup>[2]</sup>

A similar configuration but with transistors of opposite type (one NPN and one PNP) is the Sziklai pair, sometimes called the "complementary Darlington."

### **Behavior**

ㅁ

View of the chip in an MJ1000

A Darlington pair is like a set of feeders with a high current gain (approximately the product of the gains of the two transistors). In fact, integrated devices have three leads (B, C and E), broadly equivalent to those of a standard transistor.

A general relation between the compound current gain and the individual gains is given by:

$$\beta_{\text{Darlington}} = \beta_1 \cdot \beta_2 + \beta_1 + \beta_2$$

If  $\beta_1$  and  $\beta_2$  are high enough (hundreds), this relation can be approximated with:

$$\beta_{\text{Darlington}} \approx \beta_1 \cdot \beta_2$$

Darlington pairs are available as integrated packages or can be made from two discrete transistors;  $Q_1$  (the left-hand transistor in the diagram) can be a low power type, but normally  $Q_2$  (on the right) will need to be high power. The maximum collector current  $I_C(max)$  of the pair is that of  $Q_2$ . A typical integrated power device is the 2N6282, which includes a switch-off resistor and has a current gain of 2400 at  $I_C$ =10A.

A Darlington pair can be sensitive enough to respond to the current passed by skin contact even at safe voltages. Thus it can form the input stage of a touch-sensitive switch.

A typical modern device has a current gain of 1000 or more, so that only a small base current is needed to make the pair switch on. However, this high current gain comes with several drawbacks.

# **Disadvantages**

One drawback is an approximate doubling of the base/emitter voltage. Since there are two junctions between the base and emitter of the Darlington transistor, the equivalent base/emitter voltage is the sum of both base/emitter voltages:

$$V_{BE} = V_{BE1} + V_{BE2} \approx 2V_{BE1}$$

For silicon-based technology, where each  $V_{BEi}$  is about 0.65 V when the device is operating in the active or saturated region, the necessary base/emitter voltage of the pair is 1.3 V.